# Impact of Structural and Doping Parameter Variations on NQS Delay, Intrinsic Gain and NF in FinFETs

# B. Lakshmi, R. Srinivasan

Abstract— This paper investigates the effect of process variations on RF metrices, non-quasi static (NQS) delay, intrinsic gain and noise figure (NF) in 30 nm gate length FinFET by performing extensive 3D TCAD simulations. Sensitivity of NQS delay, intrinsic gain and NF on different geometrical parameters, channel doping, source/drain doping are studied. The most significant parameters are found to be gate length, underlap, oxide thickness, fin width and height, source/drain doping.

*Index Terms*— FinFET, NQS delay, intrinsic gain, NF, TCAD

#### I. INTRODUCTION

Multi-gate devices are thought as a potential alternative to MOSFETs. Even though initially, many double gate devices were suggested in the area of multi-gate transistors, double gate FinFETs are considered as a serious contender for channel scaling. Because of their quasi-planar structure they are compatible with the existing CMOS technology. Since, these devices use ultrathin bodies as their channel, suppression of short channel effects (SCEs) can be achieved with undoped channels instead of the usual high doping density channels. Abundant literature was available on FinFETs [1-4].

FinFET-based analog building blocks/RF receivers have been investigated extensively [5, 6]. RF performance of FinFETs is studied [7-9]. In the above mentioned literature, the effect of fin width on unity gain cut-off frequency ( $f_t$ ) and maximum frequency of oscillation ( $f_{max}$ ) has been investigated. The source/drain series resistance in FinFETs largely limits the device RF performance, and the losses due to the gate resistance increases with reducing gate length. Nuttinck et al [10] has studied about the source/drain resistance impact on RF performance

#### Manuscript received Aug 20, 2014

- **B.** Lakshmi, School of Electronics Engineering, VIT University, Chennai, India

- **R. Srinivasan**, Department of IT, SSN College of Engineering, Chennai, India

In this paper, nine different geometrical parameters and two doping related parameters of FinFET are varied over a wide range to study their effect on NQS delay, intrinsic gain and noise figure. Next section describes the simulation environment. Section III discusses the simulation results. Finally section IV we provides conclusions.

#### II. Simulation Environment

## 2.1 Device Description

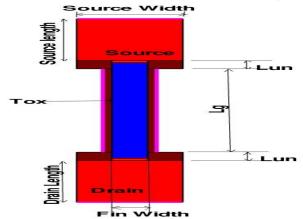

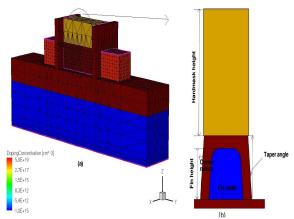

Sentaurus TCAD simulator from Synopsys [11] is used for this study. Figure 1 shows the 2D structure of the FinFET. The 3D device structure is shown in Figure 2(a). Figure 2(b) shows a 2D cut of the above 3D structure which depicts the fin cross section i.e. in Fig. 2(b) source to drain axis runs perpendicular to the page.

Figure 1: 2D structure of FinFET

Figure 2: (a) 3D structure of FinFET (b) Enlarged portion of the rounded region

# 2.2 Parameter Space

The effect of process parameters, gate length  $(L_g)$ , underlap  $(L_{un})$ , fin width (W), gate oxide thickness  $(T_{ox})$ , channel doping  $(N_{ch})$ , and source/drain doping  $(N_{SD})$  on NQS delay, intrinsic gain and NF are studied with the 2D simulations. Some of the parameters like fin height (H), source/drain cross-sectional area, fin taper angle, corner radius and hard mask height (HM) cannot be studied with 2D simulations. So these parameters are studied with 3D simulations.

Device simulator includes the appropriate models for band to band tunneling, quantization of inversion layer charge, doping dependency of mobility, effect of high and normal electric fields on mobility, and velocity saturation. The simulator was calibrated against the published results on FinFETs [12]. After calibration, the device dimensions are brought to the requirements as given in Table 1. Table 1 gives the dimensions of the nominal device and also tells the range for the various parameters studied in this paper

Table 1: Dimensions of the nominal device and their

| Process parameters                     | Nominal                             | Range of values                                                          |

|----------------------------------------|-------------------------------------|--------------------------------------------------------------------------|

|                                        | value                               |                                                                          |

| Gate length (Lg)                       | 30 nm                               | 20 nm - 40 nm                                                            |

| Fin width (W)                          | 4 nm                                | 3 nm - 10 nm                                                             |

| Fin height (H)                         | 4 nm                                | 2 nm -7 nm                                                               |

| Underlap (Lun)                         | 3 nm                                | 1 nm - 8 nm                                                              |

| Source/Drain cross<br>sectional area   | 22.5 nm <sup>2</sup>                | 16 nm <sup>2</sup> - 48 nm <sup>2</sup>                                  |

| Oxide thickness (T <sub>ox</sub> )     | 1 nm                                | 0.5 nm - 3 nm                                                            |

| Fin-taper angle                        | 2 °                                 | 0° - 5°                                                                  |

| Corner radius                          | 1 nm                                | 0 nm - 2 nm                                                              |

| Hard mask height (HM)                  | 10 nm                               | 0 nm- 100 nm                                                             |

| Channel doping (N <sub>ch</sub> )      | 1X10 <sup>16</sup> /cm <sup>3</sup> | 1X10 <sup>15</sup> /cm <sup>3</sup> -1X10 <sup>19</sup> /cm <sup>3</sup> |

| Source/drain doping (N <sub>SD</sub> ) | 1X10 <sup>20</sup> /cm <sup>3</sup> | 1X10 <sup>18</sup> /cm <sup>3</sup> -2X10 <sup>20</sup> /cm <sup>3</sup> |

# 2.3 Simulation Methodology

The RF non-quasi-static delay in the devices is studied using transient simulation. To evaluate the small signal response, a small time varying ac signal along with a DC bias is applied to the gate. The delay between the applied gate signal and drain current is measured to get the NQS delay. The intrinsic gain can be defined as the product of trans-conductance (g<sub>m</sub>) and output resistance (R<sub>o</sub>). Noise simulation in SDEVICE is a standard AC simulation with noise models included in

the physics section. The results from the noise simulation are used to extract the noise figure which is given by

$$NF = 1 + \frac{1}{S_{I}^{s}} \left\{ S_{I}^{gg} + \left| \alpha \right|^{2} S_{I}^{dd} - 2 \operatorname{Re} \left( \alpha S_{I}^{gd} \right) \right\}$$

(1)

$$\alpha = \frac{Y_s + Y_{11}}{Y_{21}} \tag{2}$$

$S_S^I$  is the current noise spectrum of the noisy source admittance and is given by

$$S_S^I = 4k_B T \operatorname{Re}(Y_S)$$

$$S_I^{gg}$$

and  $S_I^{dd}$  are the noise current spectrums, at the

gate and drain terminals respectively,  $S_{I}^{dg}$  is the cross-correlation noise spectra between the drain and gate terminals,  $Y_{11}$  (i.e.  $Y_{gg}$ ) and  $Y_{21}$  (i.e.  $Y_{dg}$ )are the respective admittance parameters.

#### III. Results and Discussion

# 3.1 Impact on NQS Delay

The eleven different process parameters are varied one at a time, according to the range given in Table 1 and their impact on NQS delay is studied in this section. NQS delay is extracted as discussed in Section 2.3 at a frequency of 200 GHz. To reason out the simulation result, the expression given by Allen et al [13] is used. For a particular NQS delay, the NQS frequency ( $f_{NQS}$ ) is given by

$$f_{NQS} = \frac{\alpha \mu_{eff} \left( V_{GS} - V_T \right)}{2\pi L_g^2} \tag{3}$$

where  $\alpha$  is the fitting parameter depending on the accuracy required for the simulation to an NQS event,  $\mu_{eff}$  the mobility,  $V_{GS}$  the gate bias and  $V_{T}$  the threshold voltage of the transistor.

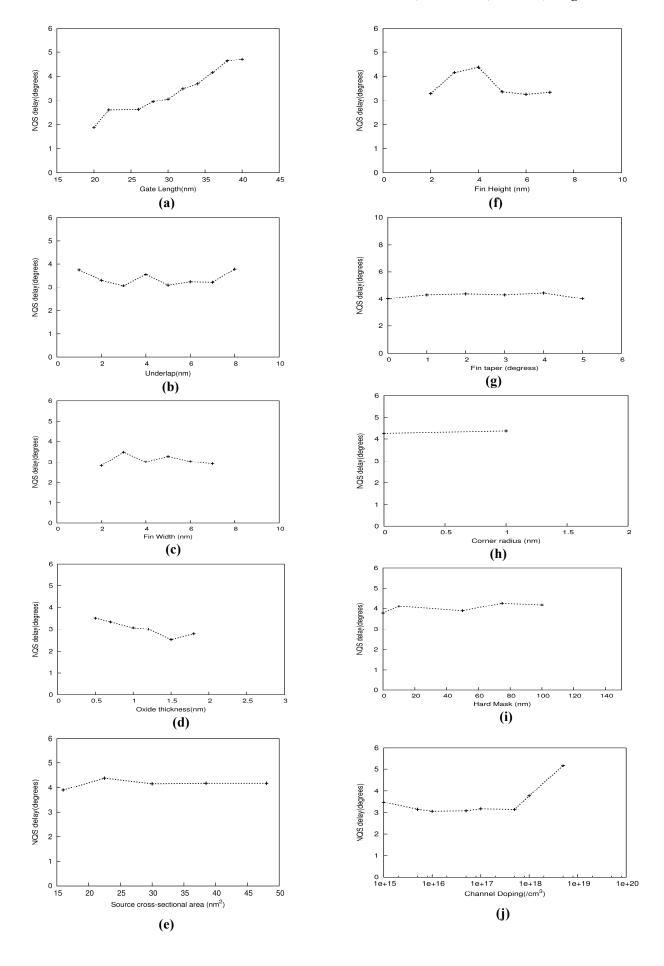

Figure 3 show the variation of NQS delay (extracted at 200 GHz) with respect to various parameters. Figure 3 (a) shows the variation of NQS delay with respect to  $L_{\rm g}$ . It can be seen that the delay increases with respect to  $L_{\rm g}$ . Equation 3 predicts that as  $L_{\rm g}$  increases  $f_{\rm NQS}$  decreases i.e. for the given frequency NQS delay increases. Figure 3(b) shows the variation of NQS delay with respect to  $L_{\rm un}$ . It can be observed that the delay increases as we move from nominal  $L_{\rm un}$ . Delay is less significant with respect to oxide thickness, fin width and height. For all other geometrical parameters, NQS delay is the least significant. Delay increases after  $1\times10^{18}/{\rm cm}^3$  for channel doping whereas it shows a decreasing trend for source drain doping.

Figure 3: (a)-(k) NQS delay versus structural and doping parameters

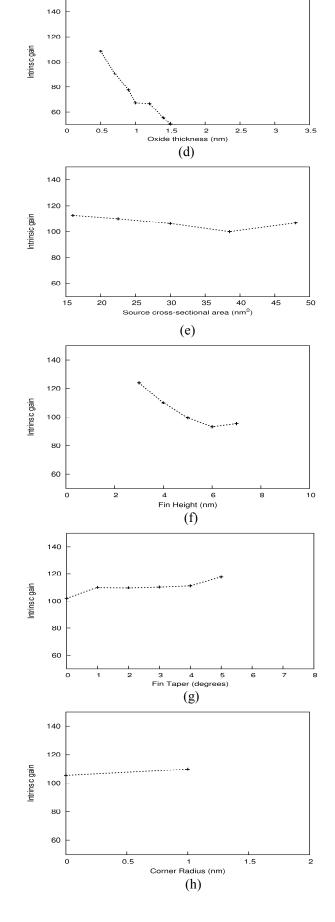

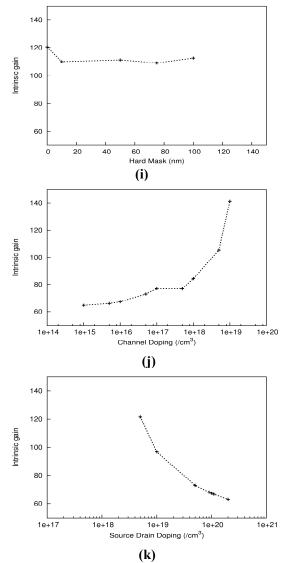

# 3.2 Impact on intrinsic gain

The different structural and doping related parameters are varied one at a time, according to the range given in Table 1 and their impact on intrinsic gain is studied in this section. Since intrinsic gain depends on both  $g_m$  and  $R_o$  their combined behavior brings the increasing or decreasing tendency with respect to the parameter variation. In the studied region,  $R_o$  dominates and decides the trends seen in the Fig. 4. For all the process parameters except source/drain cross sectional area, fin taper, corner radius and hard mask height, intrinsic gain affects significantly.

Figure 4: (a)-(k) Intrinsic gain versus structural and doping parameters

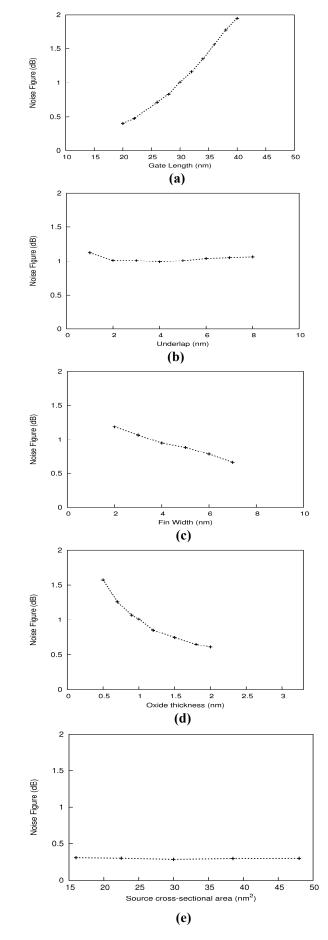

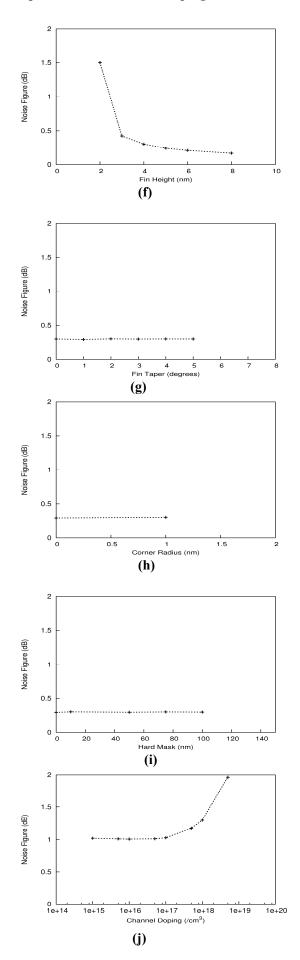

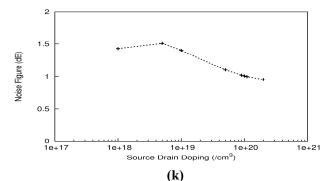

# 3.3 Impact on Noise figure

In this section the parameters are varied one at a time, according to the range given in Table 1 and their impact on noise figure is analyzed. NF is extracted using the Equation 1 as discussed in Section 2.3, at a frequency of 10 GHz. The results can be reasoned out using the following expression which relates the noise figure and  $f_t$ .

$$NF = 1 + \left(\frac{f_0}{f_t}\right)K \tag{4}$$

where  $f_o$  is the resonant frequency,  $f_t$  is the unity gain frequency and K is the noise factor scaling coefficient. It can be observed from Equation 4 that NF is inversely proportional to  $f_t$  and so the trends of various parameters with respect to noise figure. This can be evidently seen from our previous results [14]

Figure 5: (a)-(k) Noise figure versus structural and doping parameters

#### Conclusion

In this paper, the conventional FinFET device is studied for structural and doping parameter variation. Nine structural and two doping parameters are taken as input and their effect on NQS delay, intrinsic gain and noise figure have been studied. The inputs are varied over a wide range to understand the general behavior. It has been found that gate length, underlap, oxide thickness, fin height and width, and source drain doping were the most significant parameters with respect to NQS delay, intrinsic gain and NF. The least significant parameters are source/drain cross sectional area, fin taper, corner radius and hard mask height and channel doping.

## Acknowledgement

This work is supported by DRDO, Government of India

# References

- [1]B. Swahn and S. Hassoun, Gate sizing: FinFETs Vs 32 nm bulk MOSFETs, Proc. Design Automation Conference, 528–531, 2006

- [2]L. Chang, S. Tang, T.J. King, J. Bokor and C.Hu, Gate length scaling and threshold voltage control of double gate MOSFETs, Proc. IEDM,719–722, 2000

- [3]S.H. Tang, L. Chang, N. Lindert, Y.K. Choi, C.W. Lee, X. Huang, V. Subramanian, J. Bokor, T.J. King and C. Hu, FinFET-a quasi-planar double-gate MOSFET, Proc. ISSCC, 118-119,2001

- [4]J.W. Yang, P.M. Zeitzoff and H.H.Tseng, Highly manufacturable double-gate FinFET with gate-source/drain underlap, IEEE Trans. Elect. Dev. 54, 6, 1464-1470, 2007

- [5] Knoblinger, G, Fulde, M, Siprak, D, Hodel, U, Von Arnim, K, Schulz, T, Pacha, C, Baumann, U, Marshall, A, Xiong, W, Cleavelin, CR, Patruno, P and Schruefer, K, "Evaluation of FinFET RF Building Blocks", in Proc. SOI, pp. 39-40, 2007

- [6]Siprak, D, Wambacq, P, Parvais, B, Mercha, A, Fulde, M, Kruger, JV, Dehan, M and Decoutere, S "FinFET RF Receiver Building Blocks Operating Above 10 GHz", in Proc. ESSCIRC, pp. 360-363,2009

- [7] Wambacq, P, Verbruggen, B, Scheir, K, Borremans, J, Dehan, M, Linten, D, DeHeyn, V, VanderPlas, G, Mercha, A, Parvais, B, Gustin, C, Subramanian, V, Collaert, N, Jurczak, M and Decoutere, S, "The Potential of FinFETs for Analog and RF Circuit Applications", IEEE Trans. Circuits and Systems I, Vol. 54, No. 11, pp. 2541-2551, 2007.

- [8] Lederer, D, Parvais, B, Mercha, A, Collaert, N, Jurczak, M, Raskin, JP and Decoutere, S "Dependence of FinFET RF performance on fin width", in Proc. SiRF, pp. 8-11,2006

- [9]Lin, PH, Lin, JT, Eng, YC and Yu-Che Chang, "RF Performance of the Novel Planar-Type Body Connected FinFET Fabricated by Isolation-Last and Self-Alignment Process", in Proc. ULIS, pp. 1-4, 2011.

- [10] Nuttinck, S, Parvais, B, Curatola, G and Mercha, A, "Double-gate FinFETs as a CMOS technology downscaling option: An RF perspective", IEEE Trans. Elect. Dev., Vol. 54, No. 2, pp. 279-283, 2007

- [11] Synopsys Sentaurus user guide, 2012-13

- [12] Yasser M. Sabry, Tarek M. Abdolkader, Wael Fikry Farouk, "Quantum Transport Based Simulation and Design Optimization of a 10 nm FinFET", 4th International Conference on Design & Technology of Integrated Systems in Nanoscale Era, DTIS '09, on page(s): 125-129, 6-7,2009

- [13] Allen, F-L Ng, Ko, PK and Chan, M, "Determining the onset frequency of non-quasi-static effects of the MOSFET in ac simulation". IEEE Elect. Dev. Letters", Vol. 23 No. 1, pp. 37-39, 2 002.

- [14] B. Lakshmi and R. Srinivasan, "3D-TCAD Simulation Study of Process Variations on f<sub>t</sub> in 30 nm Gate Length FinFET", Proceedings in IEEE digital library, March 2011