### Agnihotram srinivas kumar, M.Sridhar

Abstract— In this project six rules for designing hybrid cascaded multilevel inverters with simplified supply and low switching losses have been derived. These design rules constrain the ratio between the dc voltages of the supplied cells and the dc voltages of the unsupplied cells. They allow one to design single-and three-phase inverters that can be operated either with staircase or with PWM. New configurations that increase the flexibility for choosing suitable switches. The concept of energy balance domain has been introduced to characterize the achievable operating modes and power factor.

Hybrid asymmetrical cascade multilevel inverters, they combine cells of different voltage ratings different topologies, or even combine switch converters with linear amplifiers. So, in this project mainly focused on the design and control of high-resolution, high-efficiency multilevel inverters with simplified dc power supplies. It introduces several rules for systematically designing the dc voltages of the cells, for which all unsupplied capacitor voltages can be regulated. Six classes of inverters are obtained covering single and three phase, staircase and pulse width-modulated (PWM) inverters.

New configurations of hybrid cascade multilevel inverters are obtained for each class. A double modulation strategy with two different frequencies is proposed that allows switching losses of PWM inverters to be reduced. Decoupled mechanisms are proposed for the total and internal energy balances. It is shown how to make the design robust by taking into account conversion losses and large dc-voltage imbalances in the design and control. The entire proposed system will be tested using MATLAB/SIMULINK.

Index Terms— AC-DC power converters, asymmetrical multilevel inverters, cascade multilevel inverters, hybrid multilevel inverters, multilevel converters, multilevel topologies, pulse width modulation converters, series connected converters.

### I. INTRODUCTION

Multilevel inverters have attracted interest for increasing the operating voltage of power conversion devices far beyond the blocking voltage of single switching devices and also for reducing the distortion of the waveforms applied to the load. Among the available topologies cascade multilevel inverters are conceptually the simplest as they combine standard

H-bridge inverters in series. Hybrid asymmetrical cascade multilevel inverters, however, present many challenges as they combine cells of different voltage ratings, different topologies, or even combine switch converters with linear amplifiers.

The main idea behind the hybrid asymmetrical cascade

Manuscript received February 05, 2015.

inverter concept is to obtain a better inverter by hybridizing the properties of several cells and switches. In particular, the combination of slow switches, featuring high blocking voltage capabilities and low relative conduction losses, with

fast switches, featuring low switching losses aims at obtaining a hybrid inverter with better equivalent switches that would feature fast switching capability, low conduction losses, and low switching losses. By operating the high-voltage cells at reduced switching frequency, far below the pulse width modulation (PWM) frequency, performing the PWM only with the low-voltage cells, the conversion losses of the inverter alone can indeed be reduced. The main property supporting this result is that the transitions between most pairs of levels involve only the transition of the low-voltage cell. This cannot, however, be achieved for all topologies for all operating points. By designing and controlling the inverter appropriately, it is, however, possible to modulate all pairs of adjacent levels by switching only the low-voltage cells. It has to be noted that the ideas formerly developed for quasi linear amplifiers are conceptually very similar and mathematically yield exactly the same design and control strategies. The concepts for obtaining reduced switching losses have been optimized and generalized for single-phase inverters by the introduction of optimized transition graphs in the switching-state space [9] and for three-phase inverters by introducing the concept of modulation domain.

The supply issues have attracted the attention of many researchers. Rich and Pinero derived design rules for canceling passively the circulation of power between the cells, in order to allow the supply with only rectifiers. Mariethoz and Rufer proposed an efficient multisource dc-dc converter to reduce supply losses. Du et al. investigated how to apply programmed PWM in the context of partially supplied inverter. Lu and Corzine proposed the use of a topology where a motor load serves as isolation between the dc links of two NPC inverters. Steimer and Manirekar proposed a topology that combines three-phase neutral point clamped (NPC) with unsupplied filtering floating H-bridge cells. Veenstra and Rufer investigated active charging and balancing strategies for this topology based on the control of common mode harmonics. The two main innovations in are the use of a three-phase inverter with a common dc-link as high-voltage cell, and the use of the low-voltage cell only as filtering devices, such that they do not require any additional

This project unifies and completes these works by establishing a theory for systematically designing hybrid cascaded multilevel inverters with simplified dc power supply and low losses. It derives a set of design rules that defines six

classes of inverters for which an active balance and an efficient modulation can be applied. Inverters with staircase (low frequency) modulation and inverters with PWM (high frequency) are designed in different ways. For the latter, the design rules are extended to take into account losses and voltage imbalances to obtain robust solutions. This project outlines the control of the resulting topologies. The proposed concepts apply for arbitrary reference voltages and currents, not only for sine waves. Finally, the performance of some selected topologies is investigated numerically and experimentally.

# II. HYBRID CASCADED MULTILEVEL INVERTER MODEL

### A. Investigated Hybrid Cascaded Multilevel Inverter Topologies

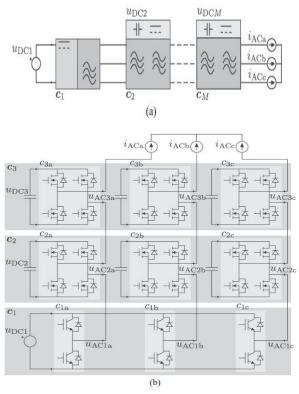

This paper investigates the design and control of singleand three-phase hybrid cascaded multilevel inverter topologies for which at least two rows have different voltage ratings and switch technologies and for which only the row with the highest voltage is supplied. Examples of such topologies are represented in Fig.1. For the three-phase topologies,we only consider structures that combine a supplied three-phase cell with unsupplied single-phase cells as for the topologies represented in the following figure.

Fig. 1. Investigated three-phase inverter topologies combine one three-phase cell with single-phase cells and thus feature a single dc supply.

- (a) General three-phase topology.

- (b) Hybrid inverter with two-level three-phase inverter and H-bridges.

The regulation of the voltages of all unsupplied capacitors in these topologies is complex for two main reasons: First, the

energy is stored in capacitors that are distributed both over the phases of the inverter and over the cells within a phase. Second, due to the asymmetry of the dc-voltages, the cells of different voltage ratings need to be coordinated to generate the desired output voltage.

For the analysis, the converter is first split between its supplied sub-inverter, which is referred to as the high-voltage cell and its unsupplied sub-inverter, which is referred to as the low-voltage cell. The main difficulty is the energy balance of the low-voltage cell.

### **B.** Necessary Conditions for Energy Balance

There are two necessary conditions for regulating the DC voltages of all unsupplied capacitors to their reference value, while tracking the reference voltage and current trajectories.

- 1) The total low-voltage cell energy can be regulated only if the low-voltage cell does not provide any active power on average. The high-voltage cell must, therefore, provide the total power on average, while the low-voltage cell can only provide reactive, harmonic, and transient powers.

- 2) The dc-voltages can be regulated only if the distribution of energy within the low-voltage cell over its phases and rows can be modified, while preserving the inverter target output voltage.

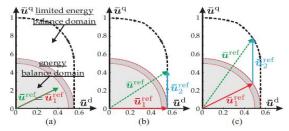

Fig.2.Voltage breakdown on average in the dq plane oriented on load current. Mode of operation depends on reference magnitude.

These conditions limit the operating range of the converter, and require special design and control procedures that will be developed in Sections III–VI.

### C. Operating Modes

The first necessary condition for balancing the total low voltage cell energy requires the high- and low-voltage cells to operate in one of the modes below.

- 1) For space-vector references smaller than the high-voltage cell maximum magnitude, the high-voltage cell is able to provide the full-voltage on average; the low-voltage cellonly needs to provide harmonic filtering that allows it toprecisely generate the reference [see Fig. 2(a)].

- 2) For space-vector references exceeding the high-voltage cell maximum magnitude, the maximum power factor can be reached by keeping the high-voltage cell contribution parallel to the current, while the low-voltage cell provides a voltage contribution orthogonal to the space-vector current on average, in order to increase the inverter achievable voltage magnitude [see Fig. 2(b)].

- 3) The maximum magnitude can be reached by contributing to the orthogonal component of the voltage with both high voltage and low-voltage cells:

the achievable power factor is lowest in this mode [see Fig. 2(c)].

The analysis of these operating modes leads to two definitions that will be useful through our developments.

- 1) Energy balance domain: This is the set of voltage vectors, represented in light gray in Fig. 2, that can be reached by the high-voltage cell alone on average. There is no or little restriction on the current waveform for trajectories fully belonging to this set. If the converter were only operated in this region, the capacitor could be very small, ideally close to zero. For steadystate operation, a larger set can be defined that corresponds to the set of voltages for which any power factor can be achieved, that is represented in Fig. 2 by augmenting the previous set with the dark gray area.

- 2) Limited energy balance domain: This is the set of voltages vectors that can be reached by the converter but that are not in the energy balance domain, represented by the area below the black bold dash curve in Fig.2. The current trajectory for these vectors must be cyclic and fulfills some restrictions. In steady-state operation, this corresponds to a restriction on the

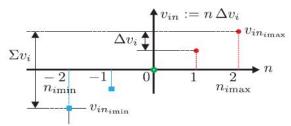

Fig.3. Key parameters defining the properties of a multilevel cell.

achievable power factor and magnitude. In this domain, the ability to exchange power between phases is very limited. The capacitors, therefore, need to be sufficiently large to ensure that the voltage ripple remains small while storing the energy required for providing reactive and harmonic power over each cycle. It should be noted that since the generation of reactive currents does not need any active power (on average), the capability of the inverter will always be higher in the q-axis as suggested in Fig.2. The maximum achievable magnitude, i.e., the size and shape of the limited energy balance domain depends on the topology and the selected configuration (see Section VII-B for further details on this aspect).

### III. DESIGN CONDITIONS FOR ENERGY BALANCE

To balance the low-voltage cell total energy, it is sufficient to operate the converter in one of the three modes described previously in Section II-C. To achieve this, while ensuring that the target space vector is generated at the output of the converter, it is necessary to follow the design rules that will be derived in this section. The keys underlying total and internal balance, while guaranteeing the tracking of the reference level trajectory, independently of the current trajectory, are the design and exploitation of redundant space vectors to adjust the cell power flows. To simplify the explanations, we will consider two series-connected cells, without loss of generality, since we can repeat the reasoning by associating two series-connected cells in a larger cell that would become the new low-voltage cell in the reasoning. In addition, we will exploit the latter property to derive the results presented in

Section VIII. We will first derive the design rules for single-phase inverters and then for three-phase inverters.

### A. Single-Phase Energy Balance Design Condition

$$c_{ij} \qquad \qquad N_i \\ \Delta v_i \\ \Delta v_i = u \text{DC}_i \qquad n \\ c_{ij} \qquad v_{in} = n \Delta v_i \qquad n \\ \begin{bmatrix} n_{i\min}, \ n_{i\max} \end{bmatrix} \\ i \qquad \qquad i \in \{1, \dots, M\} \\ M \qquad \qquad j \\ j \in \{\text{a, b, c}\} \qquad \qquad v_{in} \\ j \qquad \qquad i \\ u \text{AC}_{ij} \\ s_{ij} \qquad u \text{AC}_{ij} = v_{in} \qquad s_{ij} = n \\ \end{cases}$$

$\Delta v1$ ), . . . , (NM,  $\Delta vM$ ). The topology

$$u_{\text{AC}j} = \underbrace{\sum_{i=1}^{M} u_{\text{DC}i} \, s_{ij}}_{\text{level realization } v_o} + \underbrace{\sum_{i=1}^{M} \epsilon_{\text{DC}ij} \, s_{ij}}_{\text{error } \epsilon}. \tag{1}$$

$v_o$

$v_o$

rigorously exist

$\underbrace{v_{1k} + v_{2l}}_{\text{first realization of } v_o} = \underbrace{v_{1m} + v_{2n}}_{\text{second realization of } v_o} = v_o. \tag{2a}$

$$v_{o} \quad .u_{AC2}$$

$$s_{i} = T_{abc}^{\alpha\beta} \left[ s_{ia} \quad s_{ib} \quad s_{ic} \right]^{T} \quad (4b)$$

$$v_{2l} \leq \underbrace{\lambda v_{2l} + (1 - \lambda) v_{2n}}_{\text{average contribution } \bar{u}_{AC2}} \leq v_{2n}. \quad (2b)$$

$$v_{2l} \stackrel{\alpha\beta}{=} \left[ s_{ia} \epsilon_{DCa} \quad s_{ib} \epsilon_{DCb} \quad s_{ic} \epsilon_{DCc} \right]^{T} \quad (4c)$$

$$T_{abc}^{\alpha\beta} \quad v_{2l} i_{ACj} \quad p_{ACi} = u_{ACi}^{T} i_{AC}. \quad (4d)$$

$$v_{2l} \quad v_{2n} \quad c_{i}$$

$$v_{2l} \quad v_{2n} \quad c_{i}$$

V2l

V2n iACj

V2n iACj

$v_{1k}$

v2l v2n

*V1k*+1

$$\Delta v_1 \le \frac{N_2 + 1}{2} \Delta v_2. \tag{3}$$

$\begin{bmatrix} v_{1n1m \text{ in}}, v_{1n1m \text{ a x}} \end{bmatrix}$

### B. Three-Phase Energy Balance Design Condition

$$u_{\mathrm{AC}i} = u_{\mathrm{DC}i} s_i + \epsilon_i \tag{4a}$$

# IV. DESIGN CONDITIONS FOR ENERGY BALANCE AND LOW SWITCHING LOSSES

In the previous section, design rules that guarantee sufficient redundant realizations for each level and space vectors to regulate the voltages of the low-voltage cells were derived. The modulation of redundant vectors was used to balance the cells.PWM operation of different voltage vectors to smoothly control the output voltage can readily be superimposed using the same balancing concepts, but it may result in excessive switching losses due to the operation of the high-voltage cells at the PWM frequency. Design conditions to operate the high-voltage cells at low switching frequency have already been derived for single-[9] and for three-phase inverters [10], but without considering energy balance. This section derives design rules that allow the low-voltage cell energy balance and the optimal operation of the high-voltage cell at low switching frequency.

### A.DOUBLE MODULATION PRINCIPLE

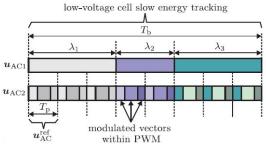

The balance principle elaborated in the previous section modulates redundant realizations of the target space vector vo with the duty cycles λr to control the low-voltage cell stored energy by manipulating the output voltage breakdown over the cells. It is worth stressing the difference between this balance modulation and the synthesis of a reference space vector voltage uref AC using PWM. The first does not affect the output voltage, while the latter requires the modulation of several space vectors with the duty cycles d. To synthesize a reference space-vector voltage uref AC using PWM, while regulating the unsupplied capacitor voltages, two modulations with two different objectives need to be combined. The modulation that regulates the dc voltages does not need to be very fast, since it deals with the balance of relatively large capacitors with long time constants, while the synthesis of the target space vector needs to be very fast since it usually deals with fast dynamics. By design, the balancing modulation requires that the high-voltage cell switches when the inverter switches from one realization of a space vector to another. In the ideal case, it would be necessary to switch the high-voltage cell space vector only at low frequency, either for the balance or when changing the set of modulated space vectors, but not during the output space-vector synthesis that would require operation at the PWM frequency. The corresponding double modulation principle is represented in Fig. 4. We will

investigate how to design the inverter to be able to apply this double modulation with two different switching frequencies in Sections IV-B and IV-C.

Fig. 4. Double modulation principle: the duty cycles  $\lambda 1, 2, 3$  that allow one to regulate the capacitor voltages and the duty cycles d1, 2, 3 that allow one to synthesize the reference are operating at two different frequencies in order to minimize the hybrid inverter switching losses.

### B. Single-Phase Energy Balance and Low-Switching Loss Design Condition

$u^{\text{ref}}$   $v_o \quad v_o + \Delta v_2$   $d \quad u^{\text{ref}}_{\text{AC}} = v_o + d \, \Delta v_2. \tag{5}$

$$v2l$$

$v2l + \Delta v2$

$$u_{ ext{AC}}^{ ext{ref}} = v_{1k} + v_{2l} + d \ \Delta v_2$$

$v_{2l} + \Delta v_2$

$$u_{\mathrm{AC}}^{\mathrm{ref}} = v_{1m} + v_{2n} + d\Delta v_2, \quad v_{1m} = v_{1k} + \Delta v_1$$

$v_{2n} \quad v_{2n} + \Delta v_2$

d

λ

# $\begin{array}{c} v_o \\ v_o \\ \text{balance energy/} \\ \text{modulation domain} \\ \text{(b)} \end{array}$

### C. Three-Phase Energy Balance and Low-Switching Loss Design Condition

$$\Delta v_1 \le (N_2 - 1)\Delta v_2$$

$$\Delta v_{i+1} \le \sum_i (N_i - 1)\Delta v_i$$

# V. THREE-PHASE LOW-VOLTAGE CELL INTERNAL BALANCE OVER PHASES

total energy

$$\bar{u}_{\text{AC1}} = \lambda v_{1k} + (1 - \lambda)v_{1m}$$

$$\bar{u}_{\text{AC2}} = \lambda v_{2l} + (1 - \lambda)v_{2n} + d\Delta v_2$$

) with the duty cycle  $\lambda$ , the

$$\begin{bmatrix} u_{ ext{AC}i ext{a}}^{\perp} & u_{ ext{AC}i ext{b}}^{\perp} & u_{ ext{AC}i ext{c}}^{\perp} \end{bmatrix} \begin{bmatrix} i_{ ext{AC} ext{a}} & i_{ ext{AC} ext{b}} & i_{ ext{AC} ext{c}} \end{bmatrix}^T = 0$$

$$\Delta v_1 \leq rac{N_2-1}{2} \Delta v_2$$

u AC $i0$

$\alpha\beta$ αβ  ${u_{\mathrm{AC}i}^{\perp}}^T i_{\mathrm{AC}} = \begin{bmatrix} u_{\mathrm{AC}i\alpha}^{\perp} & u_{\mathrm{AC}i\beta}^{\perp} \end{bmatrix} \begin{bmatrix} i_{\mathrm{AC}\alpha} & i_{\mathrm{AC}\beta} \end{bmatrix}^T = 0$ A. Compensation Through Common-Mode Voltage VI. EXPERIMENTAL RESULTS 1) Hardware Prototype:  $\Delta p_{\rm a} = u_{

m AC}i_0 i_{

m AC}a$  $\Delta p_{\rm b} = u_{{

m AC}i0} \, i_{{

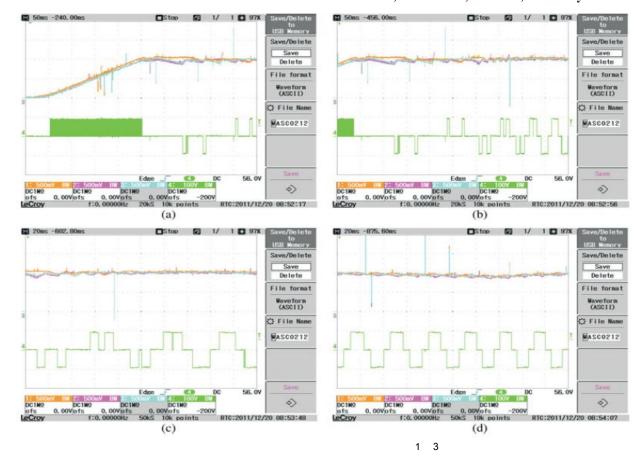

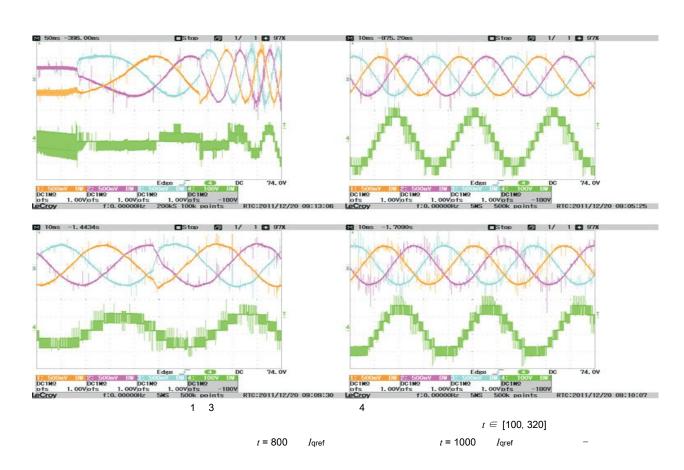

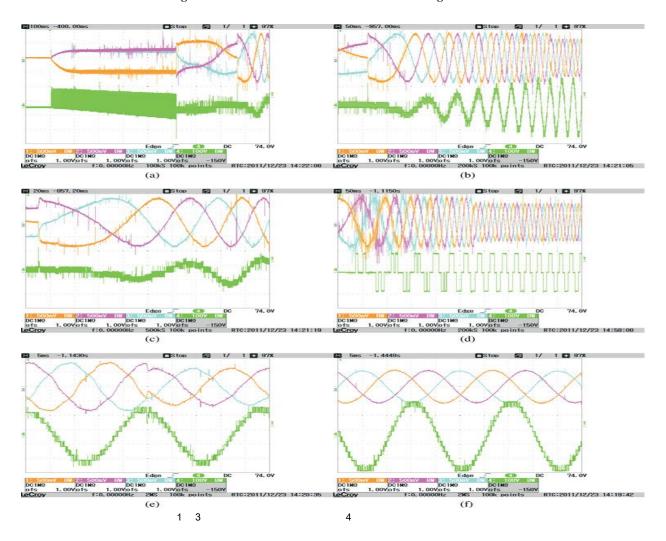

m ACb}}$  $\Delta p_{\rm c} = u_{\rm AC}i_0(-i_{\rm ACa} - i_{\rm ACb})$ uACi0 2) Software prototype: uACi0 B. Five-Level Hybrid Cascaded Multilevel Inverter Drive Results  $\min_{u_{ ext{AC}\,i0}(t)} \sum_{j \in ext{a,b,c}} e_{ij} (t+T_{ ext{h}})^2$ eij Cij t**c** 3 uDC2 =  $u_{\rm DC1} = 90$  $e_{ij}(t+T_{\mathrm{h}}) = e_{ij}(t) + \left(u_{ij}^{\mathrm{ref}}(t) + u_{\mathrm{AC}i0}(t)\right)\,i_{\mathrm{AC}j}(t)T_{\mathrm{h}}$ 1) Voltage Regulation During Precharge:  $T\mathsf{h}$ B. Compensation in the  $\alpha\beta$  Plane

### lphaeta

αβ

2) Voltage Regulation During Normal Operation:

4

$i_{qref} = 2.8$   $i_{qref} = 1.2$

6) Voltage Balance:

:

CONCLUSION

- h-bridge multilevel inverter," IEEE Trans. Power Electron., vol. 24, no. 1, pp. 25–33, Jan. 2009.

- [16] S. Mari ethoz, " 'Etude formelle pour la synth'ese de convertisseurs multiniveauxasym'etriques: Topologies, modulation et commande" Ph.D. dissertation, Ecole Polytechnique F'ed'erale de Lausanne, Lausanne (CH), Switzerland, 2005.

- [17] M. Veenstra, "Investigation and Control of a Hybrid Asymmetric Multi-Level Inverter forMedium-Voltage Applications" Ph.D. thesis, 'Ecole Polytechnique F'ed'erale de Lausanne, Lausanne (CH), Switzerland, 2003.

- [18] M. Veenstra and A. Rufer, "Non-equilibrium state capacitor voltage stabilization in a hybrid asymmetric nine-level inverter: Non-linear modelpredictive control," presented at the Eur. Power Electron. Conf., Toulouse, France, 2003.

- [19] P.W. Hammond, "Enhancing the reliability of modular medium-voltage drives," IEEE Trans. Ind. Electron., vol. 49, no. 5, pp. 948–954, Oct. 2002

- [20] J. Li, A. Q. Huang, Z. Liang, and S. Bhattacharya, "Analysis and design of active NPC (ANPC) inverters for fault-tolerant operation of high-power electrical drives," IEEE Trans. Power Electron., vol. 27, no. 2, pp. 519–533, Feb. 2012.

- [21] CHS Engineering, DAVID Development System, 2002. [Online].Available:http://www.chs-eng.ch/

### REFERENCES

- A. Nabae and H. Akagi, "A new neutral-point-clamped inverter," IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518–523, Sep. 1981

- [2] M. Marchesoni, M. Mazzucchelli, and S. Tenconi, "A non conventional power converter for plasma stabilization," in Proc. IEEE Power Electron. Spec. Conf., Apr. 1988, vol. 1, pp. 122–129.

- [3] T. Meynard and H. Foch, "Multi-level choppers for high voltage applications," EPE J., vol. 2, no. 1, pp. 45–50, 1992.

- [4] L. Delmas, T. Meynard, H. Foch, and G. Gateau, "Smc: Stacked multicell converter," in Proc. Int. Conf. Power Convers. Intell. Motion, 2001, vol. 43, pp. 63–69.

- [5] A. Damiano, M. Fracchia, M. Marchesoni, and I. Marongiu, "A new approach in multilevel power conversion," in Proc. 7th Eur. Conf. Power Electron. Appl., Jun. 1997, vol. 4, pp. 216–221.

- [6] M. D.Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high power applications," IEEE Trans. Ind. Appl., vol. 36, no. 3, pp. 834–841, May/Jun. 2000.

- [7] P. K. Steimer and M. D. Manjrekar, "Practical medium voltage converter topologies for high power applications," in Proc. IEEE Ind. Appl. Soc. Annu. Conf., Sep./Oct. 2001, vol. 3, pp. 1723–1730.

- [8] M. Veenstra and A. Rufer, "Control of a hybrid asymmetric multilevel inverter for competitive medium-voltage industrial drives," IEEE Trans. Ind. Appl., vol. 41, no. 2, pp. 655–664, Mar./Apr. 2005.

- [9] S.Mari'ethoz and A. C. Rufer, "Design and control of asymmetrical multilevel inverters," in Proc. IEEE Conf. Ind. Electron., Nov. 2002, pp. 840–845.

- [10] S. Mariethoz and A. Rufer, "New configurations for the tree-phase asymmetrical multilevel inverter," in Proc. Ind. Appl. Soc. Annu. Conf., Oct.2004, vol. 2, pp. 828–835.

- [11] O. M. Mueller and J. N. Park, "Quasi-linear IGBT inverter topologies," in Proc. Appl. Power Electron. Conf., Feb. 1994, pp. 253–259.

- [12] C. Rech and J. R. Pinheiro, "Hybrid multilevel converters: Unified analysis and design considerations," IEEE Trans. Ind. Electron., vol. 54, no. 2, pp. 1092–1104, Apr. 2007.

- [13] S. Mariethoz and A. Rufer, "Resolution and efficiency improvements for three-phase cascade multilevel inverters," in Proc. IEEE Power Electron. Spec. Conf., Jun. 2004, pp. 4441–4446.

- [14] S. Lu and K. A. Corzine, "Advanced control and analysis of cascaded multilevel converters based on p-q compensation," IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1242–1252, Jul. 2007.

- [15] Z. Du, L. M. Tolbert, B. Ozpineci, and J. N. Chiasson, "Fundamental frequency switching strategies of a seven-level hybrid cascaded