# Improvement of Power Quality Using Reduced-Rating Dynamic Voltage Restorer with a Battery Energy Storage System

# Sumathi.Badugu, G.Kaladhar, S.V.D.Anil Kumar

Abstract— In this paper, different voltage injection schemes for dynamic voltage restorers (DVRs) are analyzed with particular focus on an incipient method used to minimize the rating of the voltage source converter (VSC) utilized in DVR. An Incipient control technique is proposed to control the capacitor-supported DVR. The control of a DVR is demonstrated with a reduced-rating VSC. The reference load voltage is estimated utilizing the unit vectors. The synchronous reference frame theory is utilized for the conversion of voltages from rotating vectors to the stationary frame. The compensation of the voltage sag, swell, and harmonics is demonstrated by utilizing the reduced-rating DVR

Keywords-Dynamic voltage restorer (DVR), power quality, unit vector, synchronous reference frame, voltage harmonics, voltage sag, voltage swells

### **I.INTRODUCTION**

POWER QUALITY quandaries in the present-day distribution systems are addressed in the literature [1]-[6] due to the incremented utilization of sensitive and critical equipment pieces such as communication network, process industries, and manufacturing processes. Power quality quandaries such as transients, sags, swells, and other distortions to the sinusoidal waveform of the supply voltage affect the performance of these equipment pieces. Technologies such as custom power devices are emerged to provide bulwark against power quality quandaries [2]. Custom power contrivances are mainly of three categories such as series-connected compensators kenned as dynamic voltage restorers (DVRs), shunt-connected compensators such as distribution static compensators, and a coalescence of series and shunt-connected compensators kenned as Coalesced power quality conditioner [2]-[6]. The DVR can regulate the load voltage from the quandaries such as sag, swell, and harmonics in the supply voltages. Hence, it can for fend the critical consumer loads from tripping and consequent losses [2]. The custom power contrivances are developed and installed at consumer point to meet the puissance quality standards such as IEEE-519 [7]. Voltage sags in an electrical grid are not always possible to eschew because of the finite clearing time of the faults that cause the voltage sags and the propagation of sags from the transmission and distribution systems to the low-voltage loads Voltage sags are the main reasons for interruption in engenderment plants and for end-utilize equipment malfunctions in general. In particular, tripping of equipment in a production line can cause engenderment interruption and consequential costs due to loss of engenderment. One solution to this quandary is to make the equipment itself more tolerant to sags, either by intelligent control or by storing "ride-through" energy in the equipment. An alternative solution, in lieu of modifying each component in a plant to be tolerant against voltage sags, is to install a plant wide uninterruptible power supply system for longer power interruptions or a DVR on the incoming supply to mitigate voltage sags for shorter periods [8]-[23]. DVR scan eliminate most of the sags and minimize the jeopardy of load tripping for very deep sags, but their main drawbacks are their standby losses, the equipment cost, and withal the protection scheme required for downstream short circuits .Many

solutions and their quandaries utilizing DVRs are reported, such as the voltages in a three-phase system are balanced [8]and an energy-optimized control of DVR is discussed in [10].

For variants of voltage sags in [12] – [18]. A comparison of different topologies and control methods is presented for a DVR in [19]. The design of a capacitor-fortified DVR that bulwarks sag, swell, distortion, or unbalance in the supply voltages is discussed in [17]. The performance of a DVR with the high-frequency-link transformer is discussed in [24]. In this paper, the control and performance of a DVR are demonstrated with a reduced-rating voltage source converter (VSC). The synchronous reference frame (SRF) theory is utilized for the control of the DVR.

#### II. OPERATION OF DVR

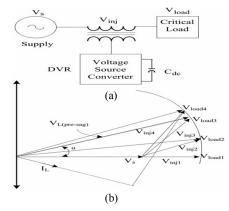

The schematic of a DVR-connected system is shown in Fig.1(a). The voltage  $V_{\rm inj}$  is inserted such that the load voltage V load is constant in magnitude and is undistorted, albeit the supply voltage Vs is not constant in magnitude or is distorted Fig.1(b) shows the phasor diagram of different voltage Injection schemes of the DVR.V\_L(pre–sag)is a voltage across the critical load prior to the voltage sag condition. During the voltage sag, the voltage is reduced to Vs with a phase lag angle of  $\theta$ . The DVR injects a voltage such that the load voltage Magnitude is maintained at the pre-sag condition prior to the voltage sag condition. During the voltage sag, the voltage is reduced to Vs with a phase lag angle of  $\theta$ .

Fig. 1.(a) Basic circuit of DVR. (b) Phasor diagram of the DVR voltage injection

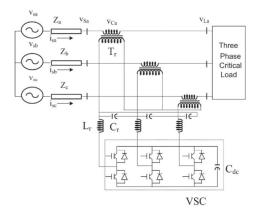

prior to the voltage sag condition. During the voltage sag, the voltage is reduced to Vs with a phase lag angle of  $\theta$ . The DVR injects a voltage such that the load voltage Magnitude is maintained at the pre-sag condition. According to the phase angle of the load voltage, the injection of voltages can be realized in four ways [19]. V<sub>inil</sub> represents the voltage injected in-phase with the supply voltage. With the injection of  $V_{inj2}$ , the load voltage magnitude remains same but it leads Vs by a minute angle. In  $V_{inj3}$ , the load voltage retains the same phase as that of the pre-sag condition, which may be an optimum angle considering the energy source [10].  $V_{ini4}$  is the condition where the injected voltage is in quadrature with the current, and this case is congruous for a capacitor-fortified DVR as this injection involves no active power [17]. However, a minimum possible rating of the converter is achieved by  $V_{injl}$ . The DVR is operated in this scheme with a battery energy storage system (BESS).Fig. 2 shows a schematic of a three-phase DVR connected tore store the voltage of a three-phase critical load. A three-phase supply is connected to a critical and sensitive load through a three-phase series injection transformer. The equipollent voltage of the supply of phase A  $V_{\rm ma}$  is connected to the point of common coupling (PCC) Vsa through short-circuit impedance  $Z_{\rm sa}$ . The voltage injected by the DVR in phase A  $V_{\rm ca}$  is such that the load voltage  $V_{\rm La}$  is of rated magnitude and undistorted .A three-phase DVR is connected to the line to inject a voltage in series utilizing three single-phase transformers Tr. Lr and Cr represent the filter components used to filter the ripples in the injected voltage. A three-leg VSC with insulated-gate bipolar transistors (IGBTs) is utilized as a DVR, and a BESS is connected

Fig.2. Schematic of the DVR-connected system.

#### A. CONTROL OF DVR

## Control of DVR With BESS for Voltage Sag, Swell, and Harmonics Compensation

The emolument for voltage sags utilizing a DVR can be performed by injecting or absorbing the reactive power or the authentic power [17]. When the injected voltage is in quadrature with the current at the fundamental frequency, the emolument is made by injecting reactive power and the DVR is with a self-fortified dc bus. However, if the injected voltage is in phase with the current, DVR injects authentic potency, and hence a battery is required at the dc bus of the VSC. The control technique adopted should consider the constraints such as the voltage injection capability (converter and transformer rating) and optimization of the size of energy storage.

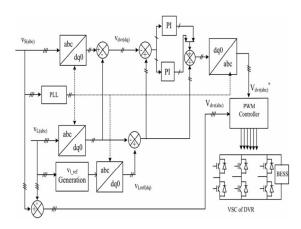

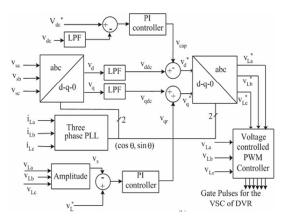

Fig. 3 shows a control block of the DVR in which the SRF theory is utilized for reference signal estimation. The voltages at the PCC  $V_S$  and at the load terminal  $V_L$  are sensed for deriving the IGBTs' gate signals. The reference load voltage  $V_L$  is extracted utilizing the derived unit vector [23]. Load voltages  $(V_{La}, V_{Lb}, V_{Lc})$  are converted to the rotating reference frame utilizing abc–dqo conversion utilizing Park's transformation with unit vectors  $(\sin\theta, \cos\theta)$  derived utilizing a phase-locked loop as

$$\begin{bmatrix} v_{L_q} \\ v_{L_d} \\ v_{L_0} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos\theta & \cos\left(\theta - \frac{2\pi}{3}\right) & \cos\left(\theta + \frac{2\pi}{3}\right) \\ \sin\theta & \sin\left(\theta - \frac{2\pi}{3}\right) & \sin\left(\theta + \frac{2\pi}{3}\right) \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix} \begin{bmatrix} v_{L_{aref}} \\ v_{L_{cref}} \end{bmatrix}$$

(1)

Similarly, reference load voltages ( $V_{La}$ ,  $V_{Lb}$ ,  $V_{Lc}$ ) and voltages at the PCC VS are additionally converted to the rotating reference frame. Then, the DVR voltages are obtained in the rotating reference frame as

$$v_{Dd} = v_{Sd} - v_{Ld} \tag{2}$$

$$v_{Dq} = v_{Sq} - v_{Lq}. (3)$$

Fig.3 Control block of the DVR that uses the SRF Method of control

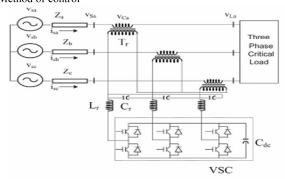

Fig.4. Schematic of the self-supported DVR.

Fig.5. Control block of the DVR that uses the SRF method of control.

The reference DVR voltages are obtained in the rotating reference frame as

$$v_{Dd}^* = v_{Sd}^* - v_{Ld}$$

(4)

$v_{Dq}^* = v_{Sq}^* - v_{Lq}$ . (5)

The error between the reference and authentic DVR voltages in the rotating reference frame is regulated utilizing two proportional – integral (PI) controllers. Reference DVR voltages in the abe frame are obtained from a reverse Park's transformation taking VDd from(4),VDq from(5), VD0 as zero as

$$\begin{bmatrix} v_{\text{dvr}a}^* \\ v_{\text{dvr}b}^* \\ v_{\text{dvr}c}^* \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta & 1 \\ \cos \left(\theta - \frac{2\pi}{3}\right) & \sin \left(\theta - \frac{2\pi}{3}\right) & 1 \\ \cos \left(\theta + \frac{2\pi}{3}\right) & \sin \left(\theta + \frac{2\pi}{3}\right) & 1 \end{bmatrix} \begin{bmatrix} v_{Dq}^* \\ v_{Dd}^* \\ v_{D0}^* \end{bmatrix}. \quad (6)$$

# International Journal of Engineering Research And Management (IJERM) ISSN: 2349-2058, Volume-02, Issue-12, December 2015

Reference DVR voltages ( $V_{dvra}$ ,  $V_{dvrb}$ ,  $V_{dvrc}$ ) and authentic DVR voltages ( $V_{dvra}$ ,  $V_{dvrb}$ ,  $V_{dvrc}$ ) are utilized in a pulse width modulated (PWM) controller to engender gating pulses to a  $V_{SC}$  of the DVR. The PWM controller is operated with a switching frequency of  $10\,\mathrm{kHz}$

B. Control of Self-Fortified DVR for Voltage Sag, Swell, and Harmonics Compensation

Fig. 4 shows a schematic of a capacitor-fortified DVR connected to three-phase critical loads, and Fig. 5 shows a control block of the DVR in which the SRF theory is utilized for the control of self-fortified DVR. Voltages at the PCC  $V_S$  are converted to the rotating reference frame utilizing abc-dqo conversion utilizing Park's transformation. The harmonics and the oscillatory components of the voltage are eliminated utilizing low pass filters (LPFs). The components of voltages in the d- and q-axes are

$$V_{d} = V_{ddc} + V_{dac}$$

(7

$$V_{q} = V_{qdc} + V_{qac}$$

(8)

The compensating strategy for compensation of voltage quality problems considers that the load terminal voltage should be of rated magnitude and undistorted. In order to maintain the dc bus voltage of the self-supported capacitor, a PI controller is used at the dc bus voltage of the DVR and the output is considered as a voltage Vcap for meeting its losses

Fig. 6. MATLAB-based model of the BESS-supported DVRconnected system

where  $v_{de}(n) = V_{de} - V_{de}(n)$  is the error between the referenced and sensed dc voltages Vdc at the nth sampling instant.  $K_{p1}$  and  $K_{i1}$  are the proportional and the integral gains of the dc

$$v_{{\rm cap}(n)} \! = \! v_{{\rm cap}(n\!-\!1)} \! + \! K_{p1} \left( v_{de(n)} \! - \! v_{de(n\!-\!1)} \right) \! + \! K_{i1} v_{de(n)} \quad (9)$$

bus voltage PI controller. The reference *d*-axis load voltage is therefore expressed as follows:

The amplitude of load terminal voltage  $V_L$  is controlled to its reference voltage  $V_L$  using another PI controller. The output of the PI controller is considered as the reactive component of voltage Vqr for voltage regulation of the load terminal voltage

.The amplitude of load voltage  $V_L$  at the PCC is calculated from the ac voltages ( $V_{L \text{cp}}, V_{L \text{c}}$ ),  $V_{L \text{c}}$ ) as

$$V_d^* = V_{ddc} - V_{Cap}$$

(10)

Then, a PI controller is used to regulate this to a reference value as

$$V_L = (2/3)^{1/2} (V_{La}^2 + V_{Lb}^2 + V_{Lc}^2)^{1/2}$$

(11)

Where  $Vte(n) = V_L - V_L(n)$  denotes the error between the reference

and actual  $V_L(n)$  load terminal voltage amplitudes at the *n*th sampling instant.  $K_{p2}$  and  $K_{l2}$  are the proportional and the integral gains of the dc bus voltage PI controller .The reference load quadrature axis voltage is expressed as follows:

$$v_{qr(n)} = v_{qr(n-1)} + K_{p2} \left( v_{te(n)} - v_{te(n-1)} \right) + K_{i2} v_{te(n)}$$

(12)

$$V_{q}^{*}=V_{qdc}-V_{qr}$$

(13)

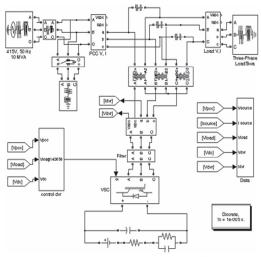

### IV. MODELING AND SIMULATION

The DVR-connected system consisting of a three-phase supply, three-phase critical loads, and the series injection transformers shown in Fig. 2 is modeled in MATLAB/Simulink environment along with a sim power system toolbox and is shown in Fig. 6. An equipollent load considered is a 10-kVA0.8-pf lag linear load. The parameters of the considered system for the simulation study are given in the Appendix

The control algorithm for the DVR shown in Fig. 3 is withal modeled in MATLAB. The reference DVR voltages are derived from sensed PCC voltages ( $V_{sa}$ ,  $V_{sb}$ ,  $V_{sc}$ ) and load voltages ( $V_{La}$ ,  $V_{Lb}$ ,  $V_{Lc}$ ). A PWM controller is utilized over the reference and sensed DVR voltages to engender the gating signals for the IGBTs of the  $V_{SC}$  of the DVR. The capacitor-fortified DVR shown in Fig.5 is withal modeled and simulated in MATLAB, and the performances of the systems are compared in three conditions of the DVR.

### V. PERFORMANCE OF THE DVR SYSTEM

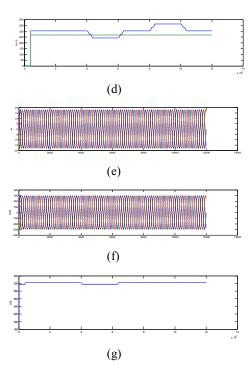

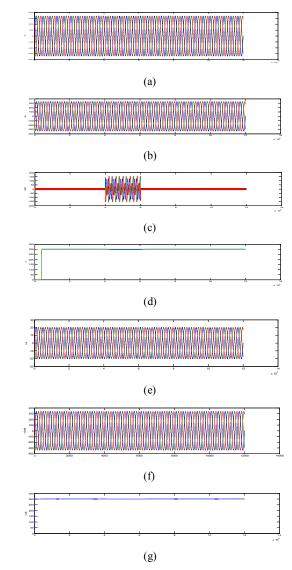

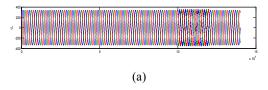

The performance of the DVR is demonstrated for different supply voltage problems such as voltage sag and swell. Fig. 7 shows the transient performance of the system under voltage sag and voltage swell conditions. At 0.2 s, a sag in supply that the load voltage is regulated to constant amplitude under both sag voltage is engendered for five cycles, and at 0.4 s, a swell in the supply voltages is engendered for five cycles. It is observed and swell

Fig.7. Dynamic performance of DVR with in-phase injection during voltage sag and swell applied to critical load

- (a) Source Voltage (b) Load Voltage (c) DVR Voltage

- (d) Source Voltage, Load Voltage (e) Source Current

- (f) Reference Load Voltage (g) dc Voltage

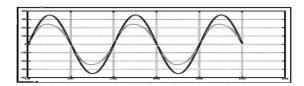

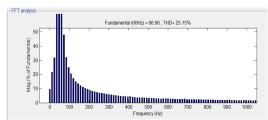

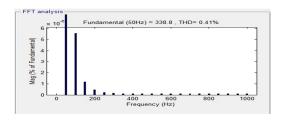

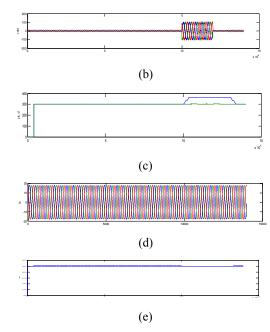

conditions both sag voltage is engendered for five cycles, and at 0.4 s, a swell in the supply voltages is engendered for five cycles. It is observed and swell conditions. PCC voltages  $V_S$ , load voltages  $V_L$ , DVR voltages  $V_C$ , amplitude of load voltage  $V_L$  and PCC voltage Vs, source currents IS, reference load voltages  $V_{Lref}$ , and dc bus voltage  $V_{dc}$  are withal depicted in Fig.7. The load and PCC voltages of phase A are shown in Fig.8, which shows the in-phase injection of voltage by the DVR. The emolument of harmonics in the supply voltage is demonstrated in Fig. 9.At 0.2 s, the supply voltage is distorted and perpetuated for five cycles. The load voltage is maintained sinusoidal by injecting felicitous emolument voltage by the DVR. The total harmonics distortions (THDs) of the voltage at the PCC, supply current, and load voltage are shown in

Fig.8 Voltages at the PCC and load terminals

Figs 9–10 respectively. It is observed that the load voltage THD is reduced to a caliber of 0.41% from the PCC voltage of 25.15%. The magnitudes of the voltage injected by the DVR for mitigating the same kinds of sag in the supply with different angles of injection are observed. The injected voltage, series current, and kilo volt ampere ratings of the DVR for the four injection schemes are given in Table I. In Scheme-1 in Table I, The in-phase injected voltage is V<sub>inj1</sub> in the phasor diagram in Fig. 1. The injection of voltage in quadrature with the line current is in Scheme-4.

Fig.9. Dynamic performance of DVR during harmonics in supply voltage applied to critical load

- (a) Source Voltage (b) Load Voltage (c) DVR Voltage

- (d) Source Voltage, Load Voltage (e) Source Current

- (f) Reference Load Voltage (g) dc Voltage

Fig.10 PCC voltage and harmonic spectrum during the disturbance

Fig.11 Load voltage and harmonic spectrum during the disturbance

|                  | Scheme 1 | Scheme 2 |

|------------------|----------|----------|

| Phase voltage(V) | 90       | 135      |

| Phase current(A) | 13       | 13       |

| VA per phase     | 1170     | 1755     |

| KVA(% of load)   | 37.5%    | 56.25%   |

Fig.12. Comparision of DVR rating for sag compensation

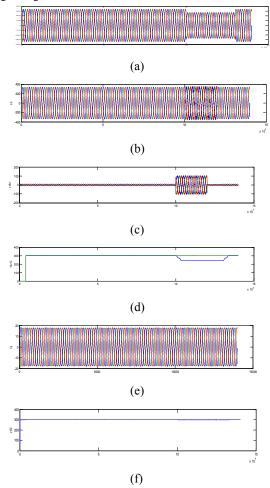

The required rating for the compensation of the same utilizing Scheme-1 is much less than that of Scheme-4. The performance of the self-fortified DVR (Scheme-4) for compensation of voltage sag and swell is shown in Fig.13 and 14. It is observed that the injected voltage is is in quadrature with the supply current, and hence, a capacitor can support the dc bus of the DVR. However, the injected voltage is higher.

Fig.13. Dynamic performance of DVR with self supported capacitor during voltage sag applied to critical load

- (a) Source Voltage (b) Load Voltage (c) DVR Voltage

- (d) Source Voltage, Load Voltage (e) Source Current

- (f) dc Voltage

Fig. 14. Dynamic performance of DVR with self supported capacitor during voltage swell applied to critical load

- (a) Load Voltage (b) DVR Voltage

- (c) Source Voltage, Load Voltage (d) Source Current

- (e) dc Voltage

### VI.CONCLUSION

The operation of a DVR has been demonstrated with a new control technique utilizing different voltage injection schemes. A comparison of the performance of the DVR with different schemes has been performed with a reduced-rating  $V_{SC}$ , including a capacitor-supported DVR. The reference load voltage has been estimated utilizing the method of unit vectors, and the control of DVR has been achieved, which minimizes the error of voltage injection. The SRF theory has been utilized for estimating the reference DVR voltages. It is concluded that the voltage injection in-phase with the PCC voltage results in minimum rating of DVR but at the cost of an energy source at its dc bus.

# REFERENCES

- M. H. J. Bollen, Understanding Power Quality Problems—Voltage Sags and Interruptions. New York, NY, USA: IEEE Press, 2000.

- A. Ghosh and G. Ledwich, Power Quality Enhancement Using Custom Power Devices. London, U.K.: Kluwer, 2002.

- M. H. J. Bollen and I. Gu, Signal Processing of Power Quality Disturbances. Hoboken, NJ, USA: Wiley-IEEE Press, 2006.

- R. C. Dugan, M. F. McGranaghan, and H. W. Beaty, Electric Power Systems Quality, 2nd ed. New York, NY, USA: McGraw-Hill, 2006.

- A. Moreno-Munoz, Power Quality: Mitigation Technologies in a Distributed Environment. London, U.K.: Springer-Verlag, 2007.

- K. R. Padiyar, FACTS Controllers in Transmission and Distribution. New Delhi, India: New Age Int., 2007.

- IEEE Recommended Practices and Recommendations for Harmonics Control in Electric Power Systems, IEEE Std. 519, 1992.

- V. B. Bhavraju and P. N. Enjeti, "An active line conditioner to balance voltages in a three phase system," *IEEE Trans. Ind. Appl.*, vol. 32, no. 2, 1. 287–292, Mar./Apr. 1996.

- S. Middlekauff and E. Collins, "System and customer impact," *IEEE Trans. Power Del.*, vol. 13, no. 1, pp. 278–282, Jan. 1998.

- M. Vilathgamuwa, R. Perera, S. Choi, and K. Tseng, "Control of energy optimized dynamic voltage restorer," in *Proc. IEEE IECON*, 1999, vol. 2, 1, 873–878

- . J. G. Nielsen, F. Blaabjerg, and N. Mohan, "Control strategies for dynamic voltage restorer compensating voltage sags with phase jump,"

in Proc. IEEE APEC, 2001, vol. 2, pp. 1267-1273.

- 12. A. Ghosh and G. Ledwich, "Compensation of distribution system voltage using DVR," IEEE Trans. Power Del., vol. 17, no. 4, pp. 1030-1036, Oct. 2002.

- 13. A. Ghosh and A. Joshi, "A new algorithm for the generation of reference voltages of a DVR using the method of instantaneous symmetrical components," IEEE Power Eng. Rev., vol. 22, no. 1, pp. 63-65, Jan. 2002.

- 14. I.-Y. Chung, D.-J. Won, S.-Y. Park, S.-I. Moon, and J.-K. Park, "The DC link energy control method in dynamic voltage restorer sys-tem," Int. J. Elect. Power Energy Syst., vol. 25, no. 7, pp. 525-531, Sep. 2003.

- 15. E. C. Aeloíza, P. N. Enjeti, L. A. Morán, O. C. Montero-Hernandez, and S. Kim, "Analysis and design of a new voltage sag compensator for critical loads in electrical power distribution systems," IEEE Trans. Ind. Appl., vol. 39, no. 4, pp. 1143-1150, Jul./Aug. 2003.

- 16. J. W. Liu, S. S. Choi, and S. Chen, "Design of step dynamic voltage regulator for power quality enhancement," IEEE Trans. Power Del., vol. 18, no. 4, pp. 1403-1409, Oct. 2003.

- 17. A. Ghosh, A. K. Jindal, and A. Joshi, "Design of a capacitor supported dynamic voltage restorer for unbalanced and distorted loads," IEEE Trans. Power Del., vol. 19, no. 1, pp. 405-413, Jan. 2004.

- 18. A. Ghosh, "Performance study of two different compensating devices in custom power park," Proc. Inst. Elect. Eng.—Gener., Transm. Distrib., vol. 152, no. 4, pp. 521-528, Jul. 2005.

- 19. J. G. Nielsen and F. Blaabjerg, "A detailed comparison of system topolo-gies for dynamic voltage restorers," IEEE Trans. Ind. Appl., vol. 41, no. 5, 1272-1280, Sep./Oct. 2005.

- 20. M. R. Banaei, S. H. Hosseini, S. Khanmohamadi, and G. B. Gharehpetian, "Verification of a new energy control strategy for dynamic voltage restorer by simulation," Simul. Model. Pract. Theory, vol. 14, no. 2, pp. 112-125, Feb. 2006.

- 21. A. K. Jindal, A. Ghosh, and A. Joshi, "Critical load bus voltage control using DVR under system frequency variation," Elect. Power Syst. Res., vol. 78, no. 2, pp. 255-263, Feb. 2008.

- 22. D. M.Vilathgamuwa, H.M.Wijekoon, and S.S.Choi, "A novel technique to compensate voltage sags in multiline distribution system—The interline dynamic voltage restorer," IEEE Trans. Ind. Electron., vol. 53, no. 5. 1603-1611, Oct. 2006.

- A. Chandra, B. Singh, B. N. Singh, and K. Al-Haddad, "An improved control algorithm of shunt active filter for voltage regulation, harmonic elimination, power-factor correction, and balancing of nonlinear loads," IEEE Trans. Power Electron., vol. 15, no. 3, pp. 495-507, May 2000.

- "Three-phase HFL-DVR with independently controlled phases," IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1706 -1718, Apr. 2012

Miss. Sumathi.Badugu received B.Tech Degree in Electrical and Electronics Engineering From Acharya Nagarjuna University, Guntur, A.P., India in 2011. Presently she is M.Tech PG Student Scholar in from Department of Electical & Electronics Engineering, St.Ann's College of Engineering

&Technology, Chirala, A.P, India. She attened various workshops and technical seminars at graduation level . She attended one international conference at SACET.Chirala.India. Her areas of interest Transmission of Distribution in power systems.

Mr.G.Kaladhar received B.Tech Degree in Electrical and Electronics Engineering from JNT University, Hyderabad in 2003 and M.Tech in power and Industrial Drives from JNT University ,Kakinada in 2006. Presently pursuing Ph.D from

Department of Electrical Engineering, SV University, Tirupathi, A.P, India. He had been working as Assistant professor in EEE Department, St. Ann's College of Engineering & Technology, Chirala, A.P, India from 2006 to till. Mr.G.Kaladhar is an author of 1 journal and attended various workshops and facaulty development programs. He is life member of MISTE Society. His area of research and study interests includes FACTS Technology, Recent Trends in Power Systems.

Mr.S.V.D.Anil Kumar received B.Tech Degree in Electrical and Electronics Engineering from SV University, Tirupathi, A.P, India in 2000. M. Tech in Power Electronics from Visveswaraiah Technological University, Belgaum, India in 2005. Presently, he is Head of the department and Associate

professor in the Department of Electrical & Electronics Engineering, St. Ann's College of Engineering & Technology, Chirala, A.P, India. He has 15 years of Teaching and industrial, Research Experience and now he is a Ph.D Research scholar in Electrical Engineering Department, JNT University, Hyderabed, India.

Mr.S.V.D. Anil Kumar is an author of more than 15 journal and conference papers. He attended and conducted various technical workshops and faculty development programs. He is Life member of ISTE, Member in IAENG, IACSI etc. his research and study interests include power quality, Harmonics in Power Systems.